VITIS_HLS 2022.1 : ap_uint range ignores MSB bit when used when chained with another operator. Compiler should throw warning.

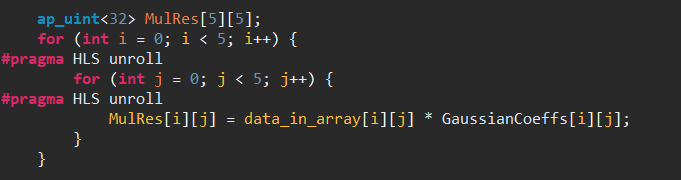

Gaussian Filter Using Vitis HLS. In my previous post, I implemented the… | by Muhammed Kocaoğlu | Medium

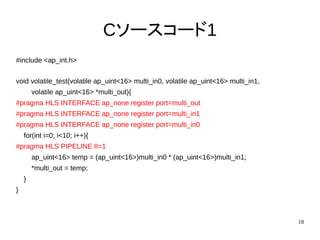

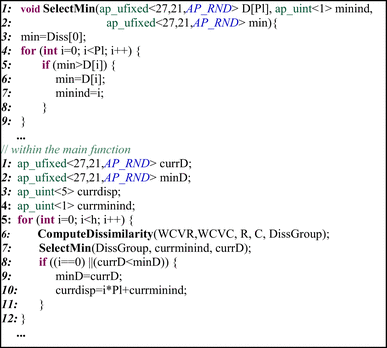

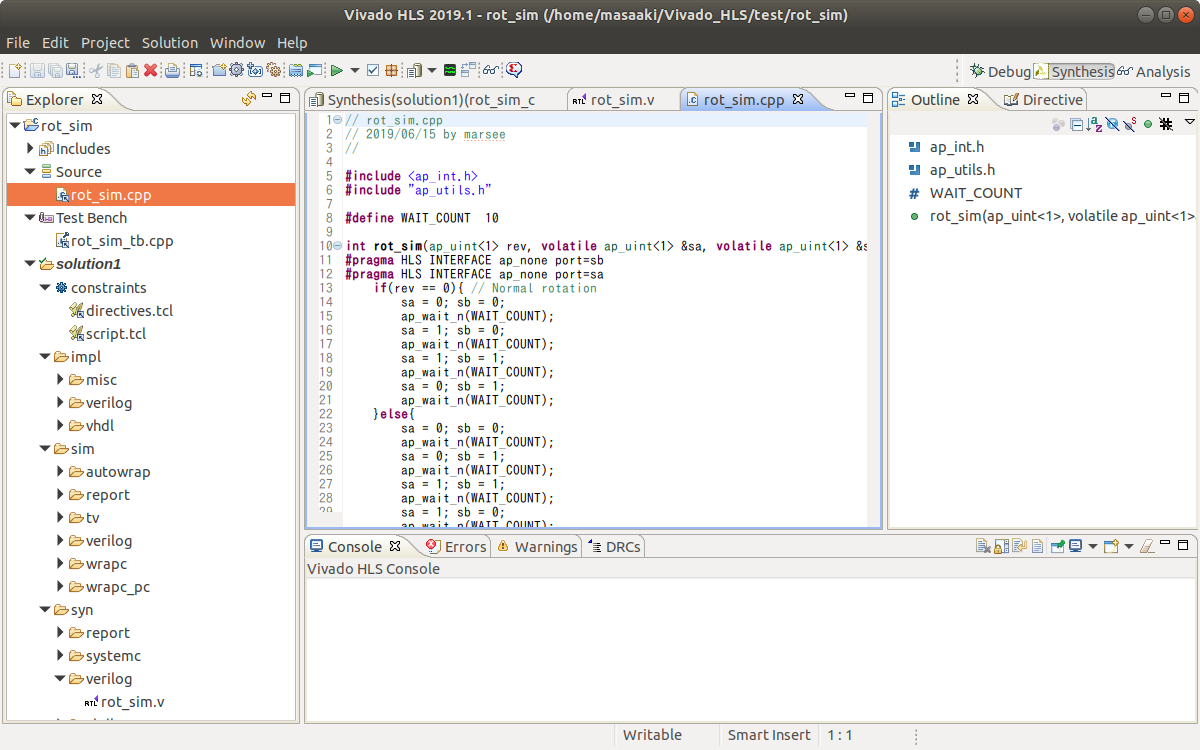

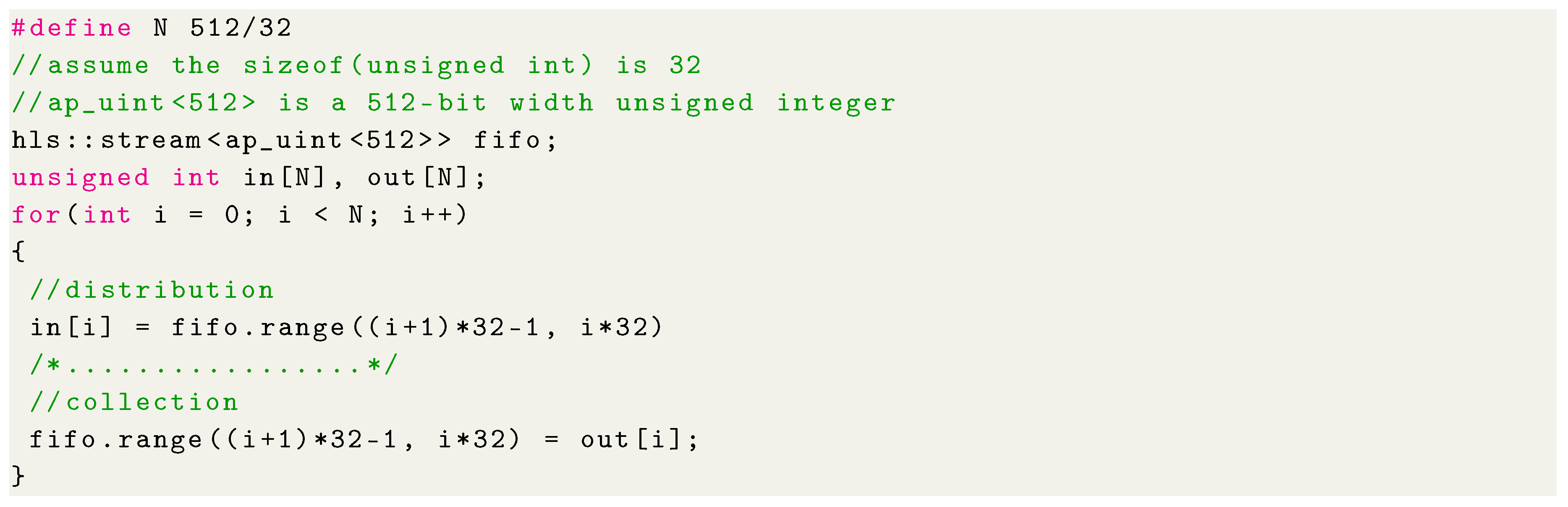

FPGA HLS Today: Successes, Challenges, and Opportunities | ACM Transactions on Reconfigurable Technology and Systems

Electronics | Free Full-Text | High-Level Synthesis Design for Stencil Computations on FPGA with High Bandwidth Memory

Automated FPGA Hardware Synthesis for High-Throughput Big Data Filtering and Transformation: An SQL query transpiler targeting Vivado HLS C++ tools for high-level stream transformation and filtering on FPGAs using Apache Arrow.

![PDF] Design Patterns for Code Reuse in HLS Packet Processing Pipelines | Semantic Scholar PDF] Design Patterns for Code Reuse in HLS Packet Processing Pipelines | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/9a13a6f8a69e8fa95d5d59f6a35bb402594e486d/3-Figure3-1.png)